开漏输出以及推挽输出详解

开漏输出以及推挽输出详解

开漏输出:开漏输出就是不输出电压,控制输出低电平时引脚接地,控制输出高电平时引脚既不输出高电平,也不输出低电平,为高阻态。如果外接上拉电阻,则在输出高电平时电压会拉到上拉电阻的电源电压。这种方式适合在连接的外设电压比单片机电压低的时候。

推挽输出:是一种使用一对选择性地从相连负载灌电流或拉电流的器件的电路。它常常使用一对参数相同的功率三极管或MOSFET管,以推挽方式存在于电路中。

1 输出

1.1 推挽输出

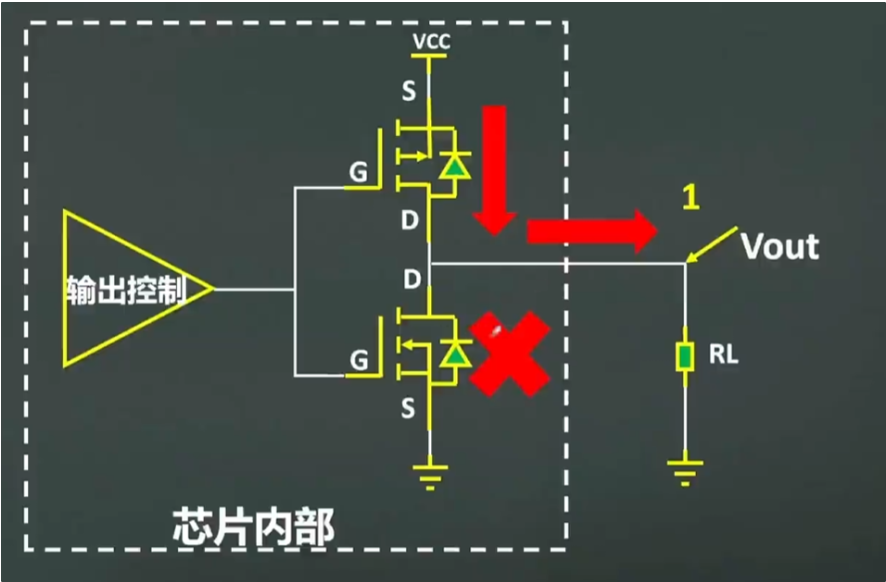

推挽输出是指 输出端口通过一个晶体管的开关来控制电平状态,推挽输出可以实现高电平和低电平两种状态。输出高电平时,NPN型晶体管导通,PNP型晶体管截止,呈现向外推的形式。(下图时MOS管,工作方式不一样,此处只做图例)

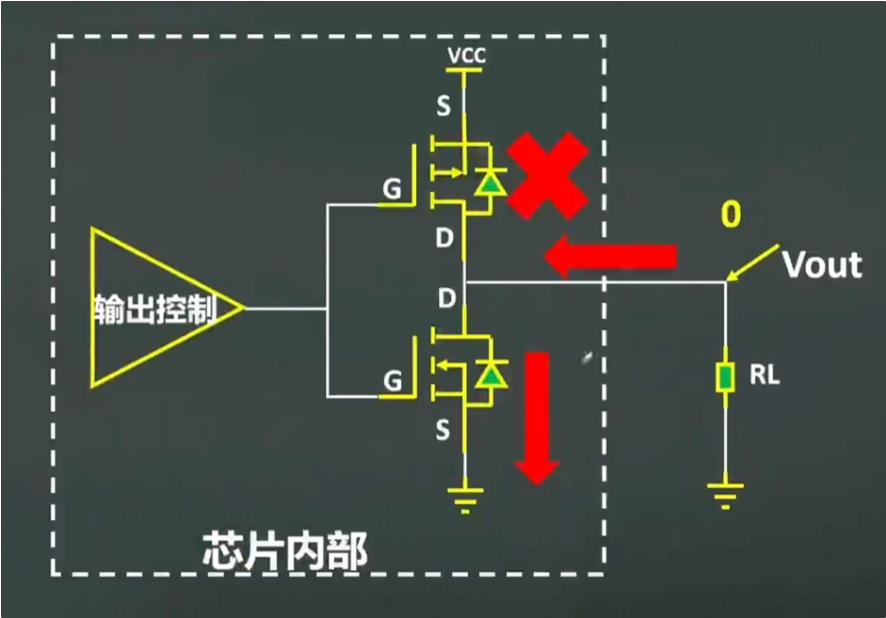

输出低电平时,PNP型晶体管导通,NPN型晶体管截止,呈现向回挽的形式。

优点:

- 输出高低电平、电源电压基本没有压差。

- 高低电平驱动能力较强,一般数字芯片推挽,输出IO口驱动电流最大可到20mA。

- 电平切换速度快。

缺点:

- 不支持线与(指两个输出不可以接到一起)。

- 如果当两个推挽输出结构相连在一起,一个输出高电平,即上面的MOS导通,下面的MOS断开时,同时另一个输出低电平,即上面的MOS断开,下面的MOS导通时。电流会从第一个引脚的VCC通过上端MOS再经过第二个引脚的下端MOS直接流向GND。整个通路上电阻很小,会发生短路,进而可能造成端口的损害。这也是为什么推挽输出不能实现线与的原因。

补充说明:推挽输出的最大特点是可以真正输出高电平和低电平,在两种电平下都具有驱动能力。所谓的驱动能力,就是指输出电流的能力。对于驱动大负载(即负载内阻越小,负载越大)时,例如IO输出为5V,驱动的负载内阻为10欧,于是根据欧姆定律可以知道正常情况下负载上的电流为0.5A(推算出功率为2.5W)。显然一般的IO不可能有这么大的驱动能力,也就是没有办法输出这么大的电流。于是造成的结果就是输出电压会被拉下来,达不到标称的5V。当然如果只是数字信号的传递,下一级的输入阻抗理论上最好是高阻,也就是只需要传电压,基本没有电流,也就没有功率,于是就不需要很大的驱动能力。

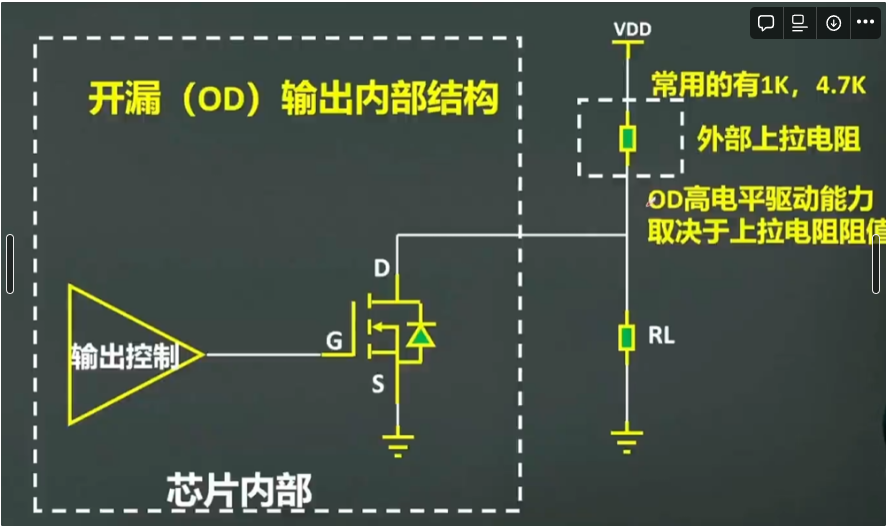

1.2 开漏输出

输出端口通过一个晶体管的开关来控制电平状态,但与推挽输出不同,开漏输出只能实现低电平状态,而不能直接输出高电平。

开漏输出的原理是,在输出端口接入一个PNP型晶体管,它的集电极连接到输出端口,发射极接地。当需要输出低电平时,晶体管导通,输出端口接地,形成低电平。当需要输出高电平时,晶体管截止,输出端口处于悬空状态,即高阻态。为了实现完整的输出功能,开漏输出通常需要结合外部上拉电阻。当输出端口处于高阻态时,外部上拉电阻将输出端口拉高至所需的高电平。因此,开漏输出可以通过控制晶体管的导通和截止来实现低电平输出,而高电平输出则由外部上拉电阻提供。开漏输出常用于多路设备共享总线的情况下,如I2C、SPI等通信协议中。通过多个开漏输出端口的组合,可以实现多路设备对总线的控制,同时避免输出冲突和电平干扰。

优点:

- 可实现电平转换,输出电平取决于上拉电阻电源。

- 可以实现IO的的线与。

缺点:

- 高电平的驱动能力差,取决于外部上拉电阻。

- 电平切换速率取决于外部上拉电阻。(上升沿的延时作用,因为上升沿是通过外接上拉无源电阻对负载充电,所以当电阻选择小时延时就小,但功耗大。反之延时大功耗小。如果对延时有要求,则建议用下降沿输出。)

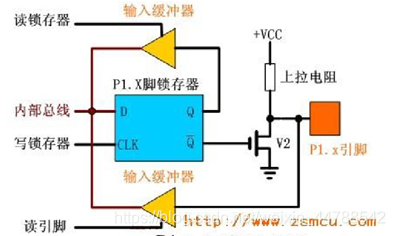

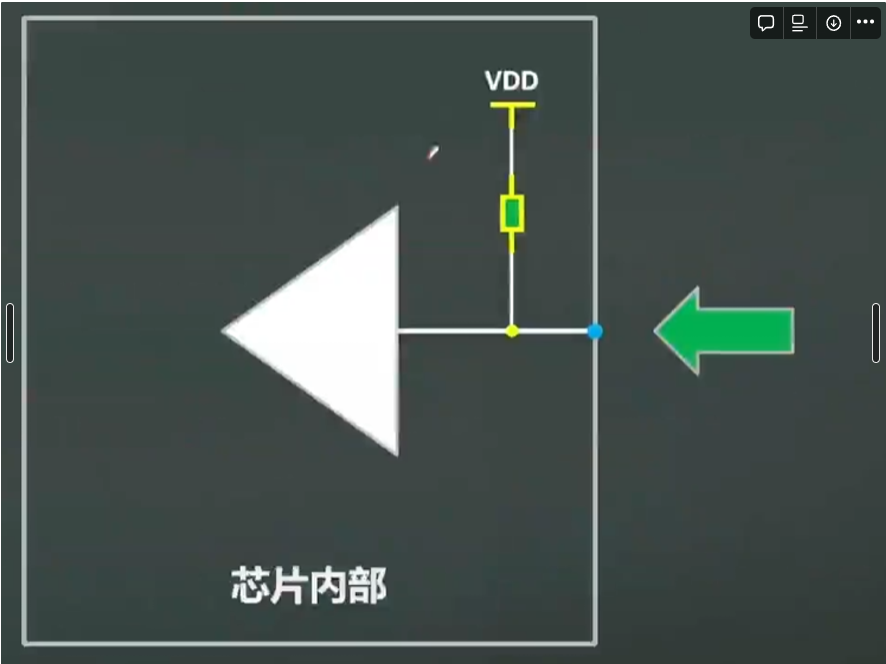

关于准双向IO,实际上结构类似于开漏输出,只不过是把上拉电阻集成到了单片机内部。

如51单片机的P1 ~ P3端口。

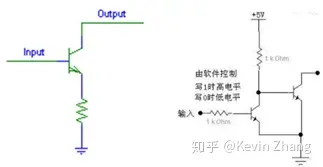

1.3 开集输出

开集输出和开漏输出原理基本类似,区别在于开漏输出使用的是MOS管,其中的 “漏” 指的是MOS管的漏极。另一个使用三极管,其中的 “集” 指的是三极管的集电极。这两者其实都是和推挽输出相对应的输出模式,由于使用MOS管的情况较多,很多时候就用 “开漏输出” 这个词代替了开漏输出和开集输出。

上图左边电路是开集(OC)输出最基本的电路,当输入为高电平时,NPN三极管导通,Output被拉到GND,输出为低电平。当输入为低电平时,NPN三极管闭合,Output相当于开路(输出高阻),此时对外没有任何的驱动能力。

上图右边的电路中多使用了一个三极管完成了”反相”,当输入为高电平时,第一个三极管导通,此时第二个三极管的输入端会被拉到GND,于是第二个三极管断开,输出高阻。当输入为低电平时,第一个三极管断开,此时第二个三极管输入端会被上拉电阻拉到高电平,于是第二个三极管导通,输出被拉到GND。这样,这个电路输入与输出是同相的了。

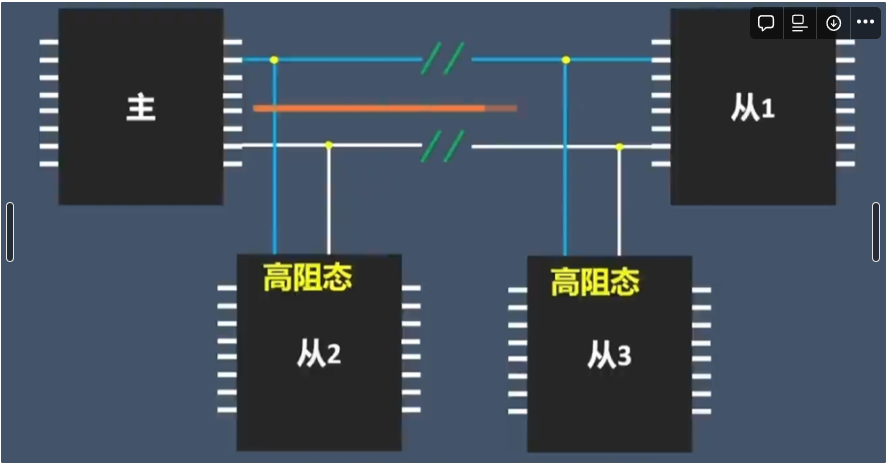

1.4 高阻态

关于开漏输出的高阻态,他通常用在总线上,当主设备与其中一个从设备相连的时候,阻断其他设备与主设备相连,即呈现出高阻态的形式。

线与:指的是多个信号直接连接再一起,只有当所有信号全部为高电平时,合在一起的总线为高电平,只要有任意一个或者多个信号为低电平,则总线为低电平。而推挽输出不行,如果高电平和低电平连在一起,会出现电流倒灌,损坏器件。

2 输入

2.1 上拉输入

是指芯片输入引脚通过电阻接到电源电压。

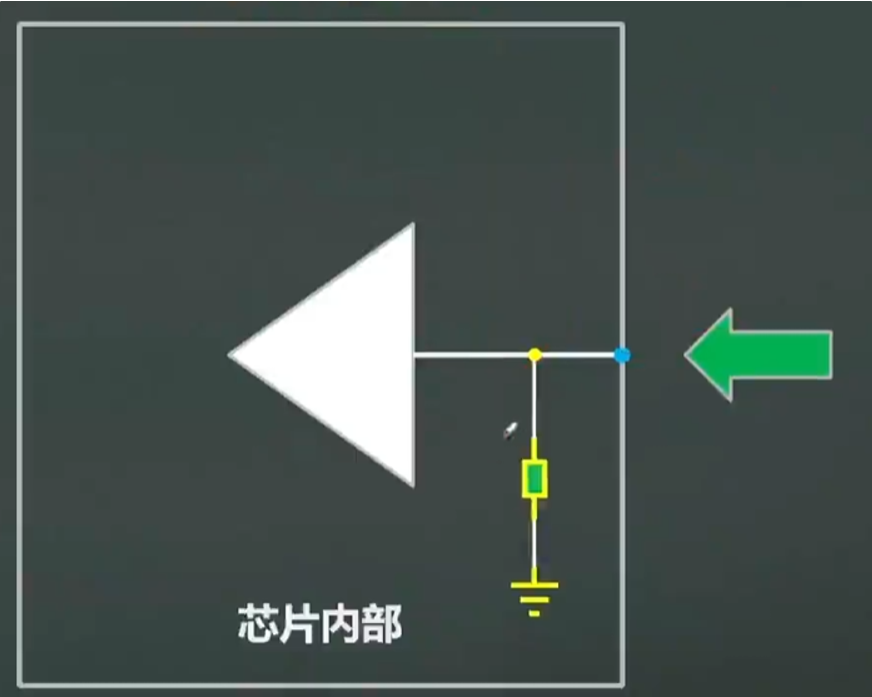

2.2 下拉输入

是指芯片输入引脚通过电阻接到参考0电平。

2.3 浮空输入

浮空输入是指将输入引脚没有连接到任何外部信号源或电路,使其处于未定义的状态。在这种情况下,输入引脚既不连接到高电平(VDD)也不连接到低电平(GND),而是处于开路状态。

浮空输入可能会导致输入信号漂移或产生不确定的结果。这是因为未连接的输入引脚可以受到周围环节中的电磁干扰,从而引起电压波动,进而影响输入状态。在某些情况下,浮空输入可能会被误认为是高电平或低电平,这取决于具体的电路设计和输入引脚的特性。

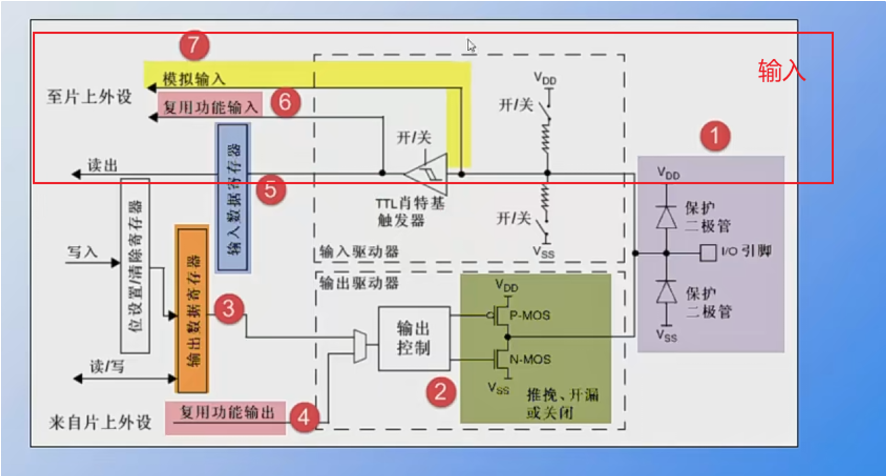

我们主要看一下他这个推挽、开漏输出的设计,P-MOS晶体管导通、N-MOS晶体管截止,呈现推。P-MOS晶体管截止、N-MOS晶体管导通,呈现挽。

当开漏状态时,只需要N-MOS管,当需要输出低电平时,晶体管导通,输出端口接地,形成低电平。当需要输出高电平时,晶体管截止,输出端口处于悬空状态,即高阻态。